# eMRAM: From Lab to Fab

CEA-Leti Memory Workshop 2017 June 27, 2017 Dave Eggleston, VP Embedded Memory

GLOBALFOUNDRIES

### Markets & Requirements

eMRAM Limitations

eMRAM Enabling Features

**Competing Solutions**

### **Cost Effective Manufacturing**

### Future eMRAM

# Markets & Requirements

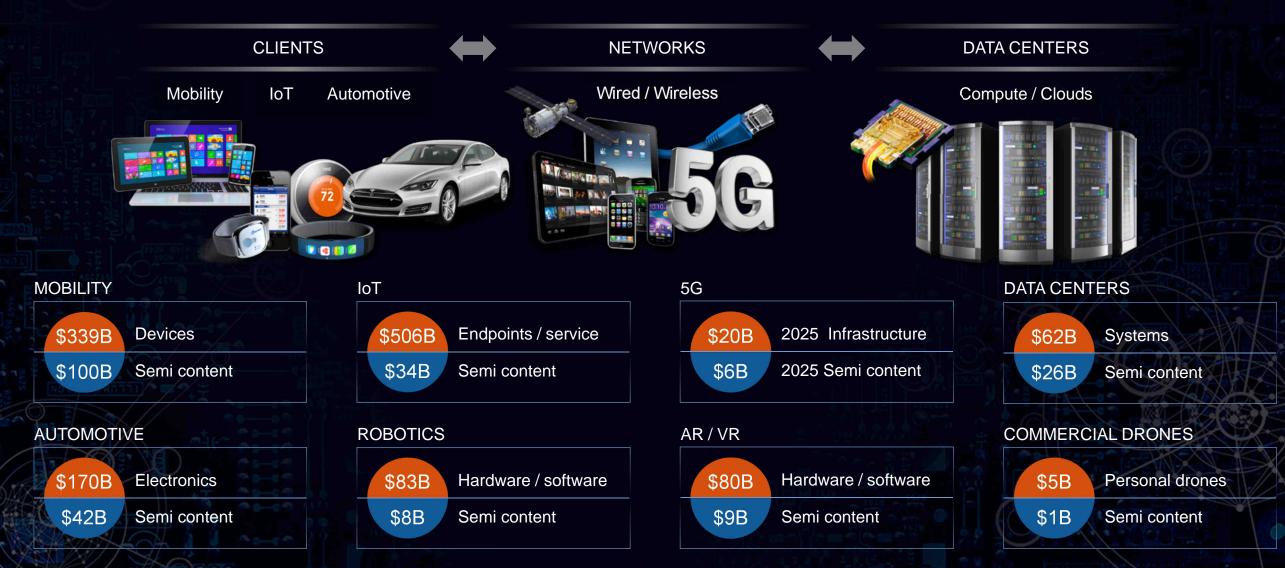

### High Volume New Markets Driving the Opportunities

All data, except for 5G, refer to 2020.

Sources: 5G: Mobile Experts; Automotive and Mobility; Average of IHS and other market research firm data; AR/VR: GLOBALFOUNDRIES analysis of Goldman Sachs, Bank of America, and some market research data; Commercial Drones, Data Centers, and IoT: GLOBALFOUNDRIES analysis and interpretation of market research data; Robotics: GLOBALFOUNDRIES analysis of Bank of America and some market research data.

### High Volume New Markets Driving the Opportunities

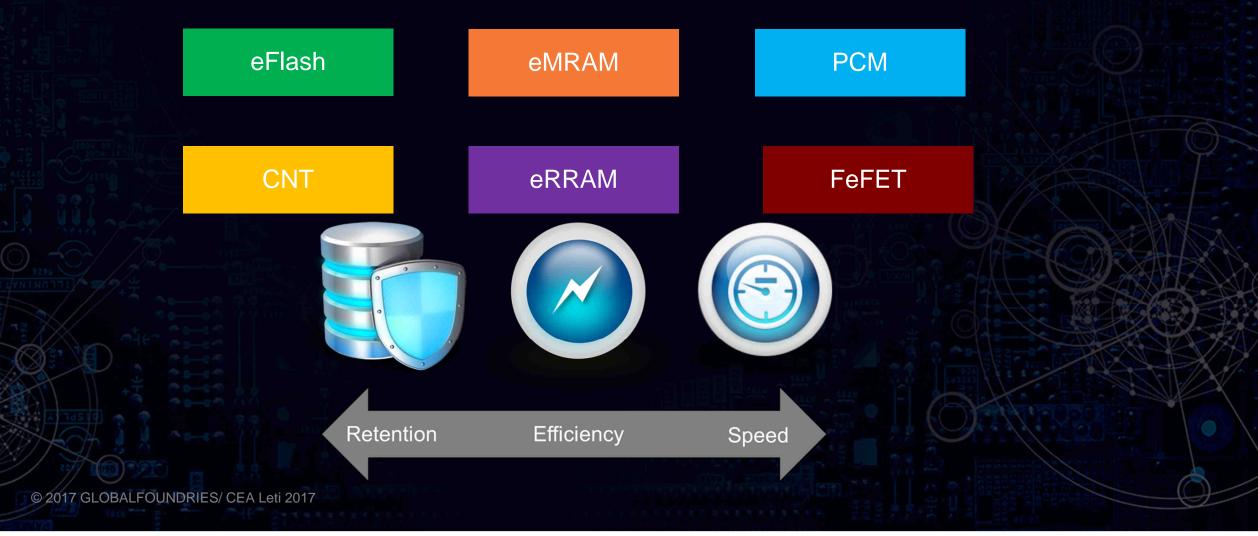

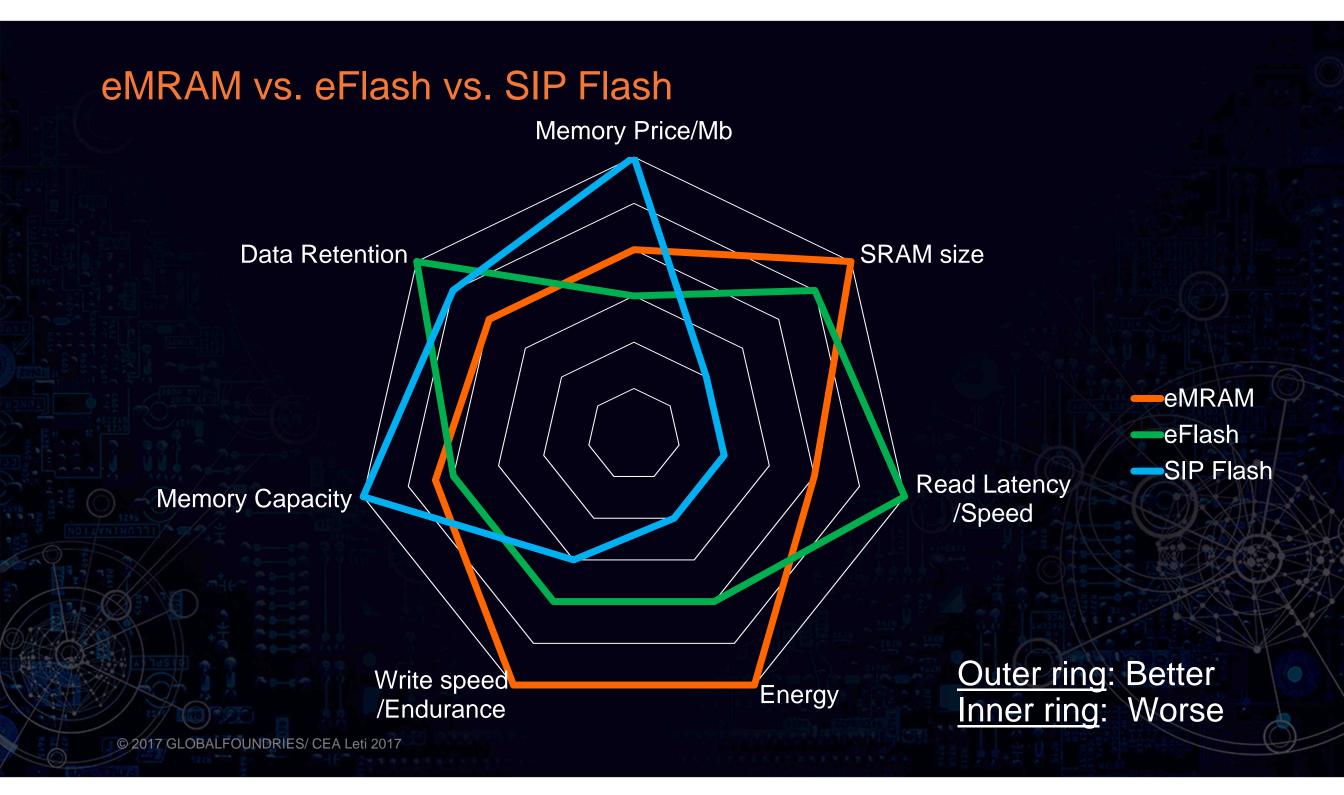

### Embedded Memory: Non-Volatile Options

#### **Embedded Memory: Non-Volatile Options**

#### eMRAM

<u>Pro:</u> speed, endurance, versatility, masks <u>Con:</u> complex stack, data retention

#### eFlash

Pro: data retention Con: speed, masks

#### eRRAM

<u>Pro:</u> simple stack, masks <u>Con:</u> speed, endurance, data retention

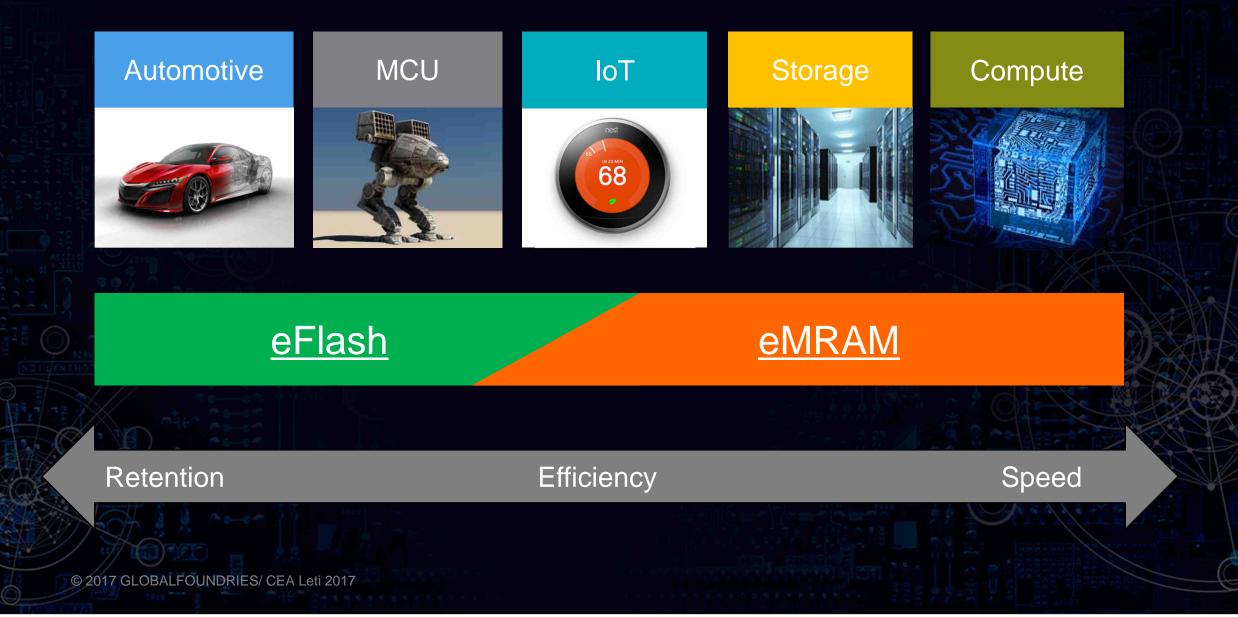

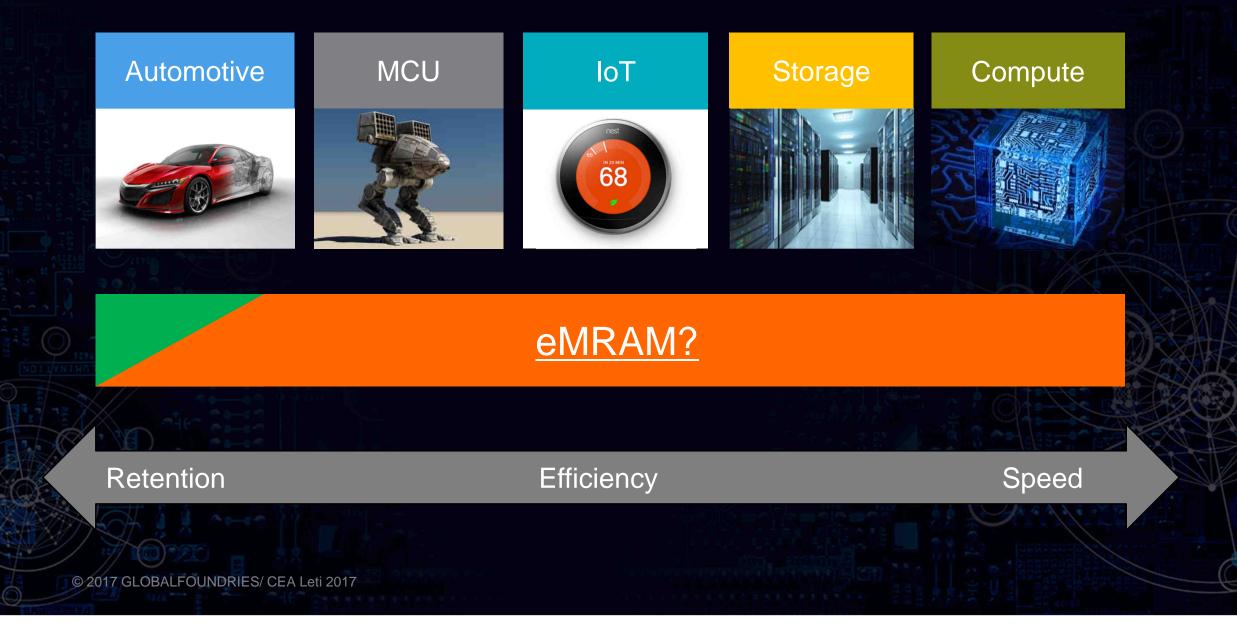

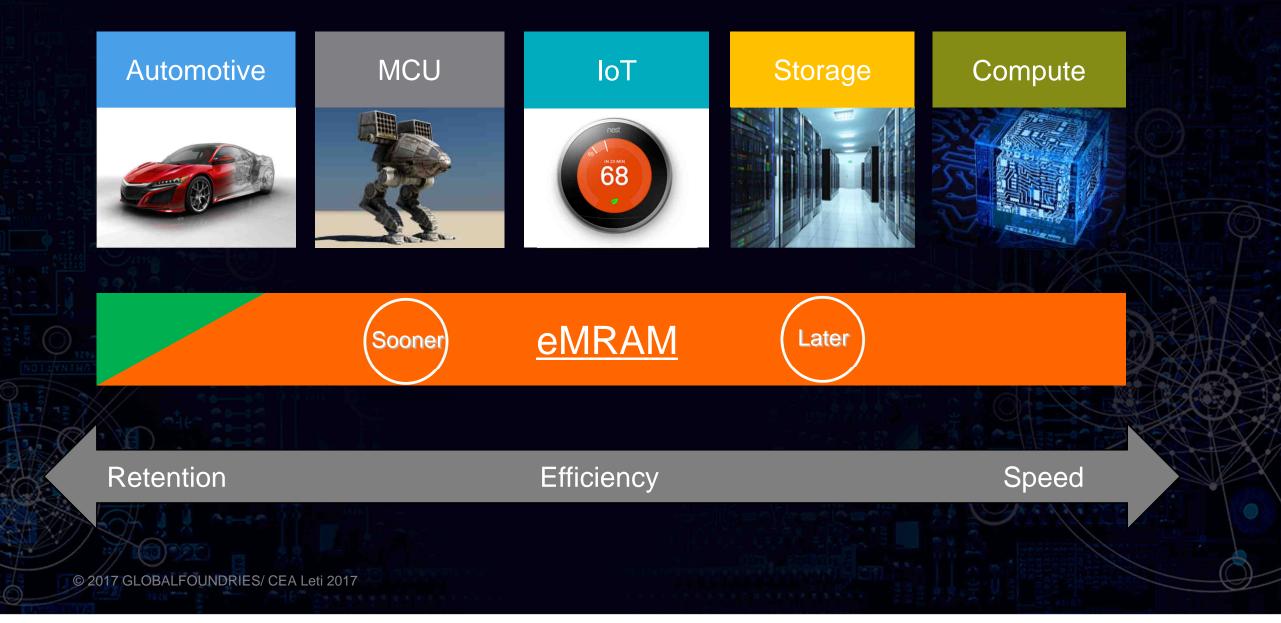

### **Embedded Memory: Application View**

### Embedded Memory: <28nm Application View

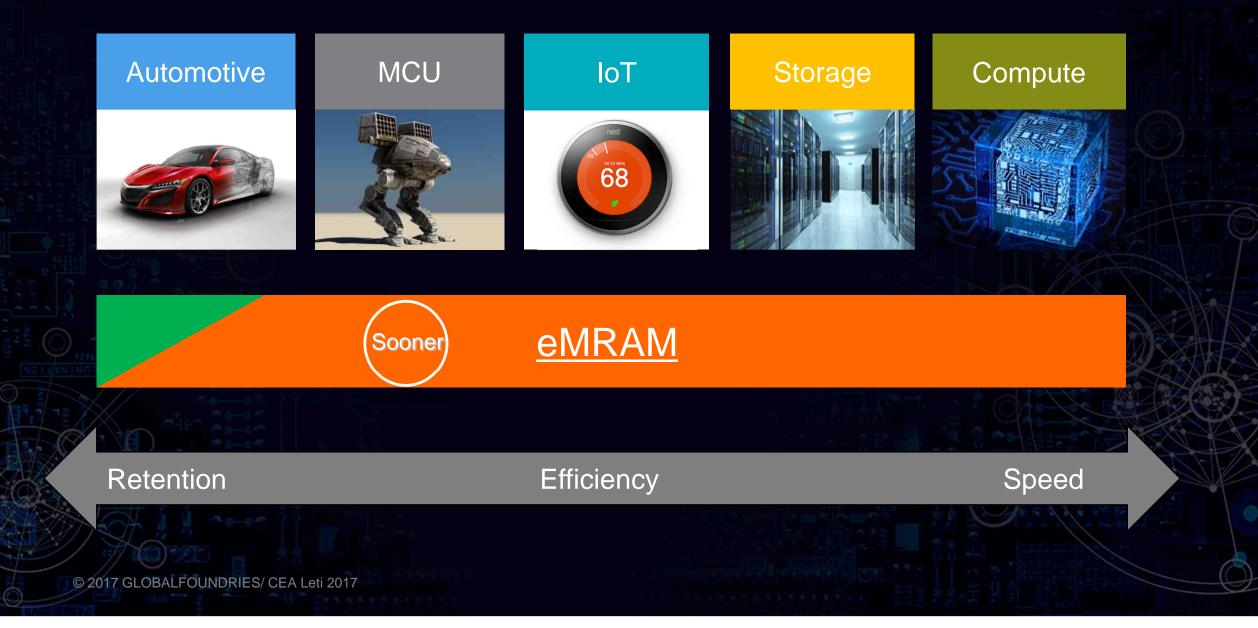

### Embedded Memory: eMRAM market timing

### Embedded Memory: eMRAM markets

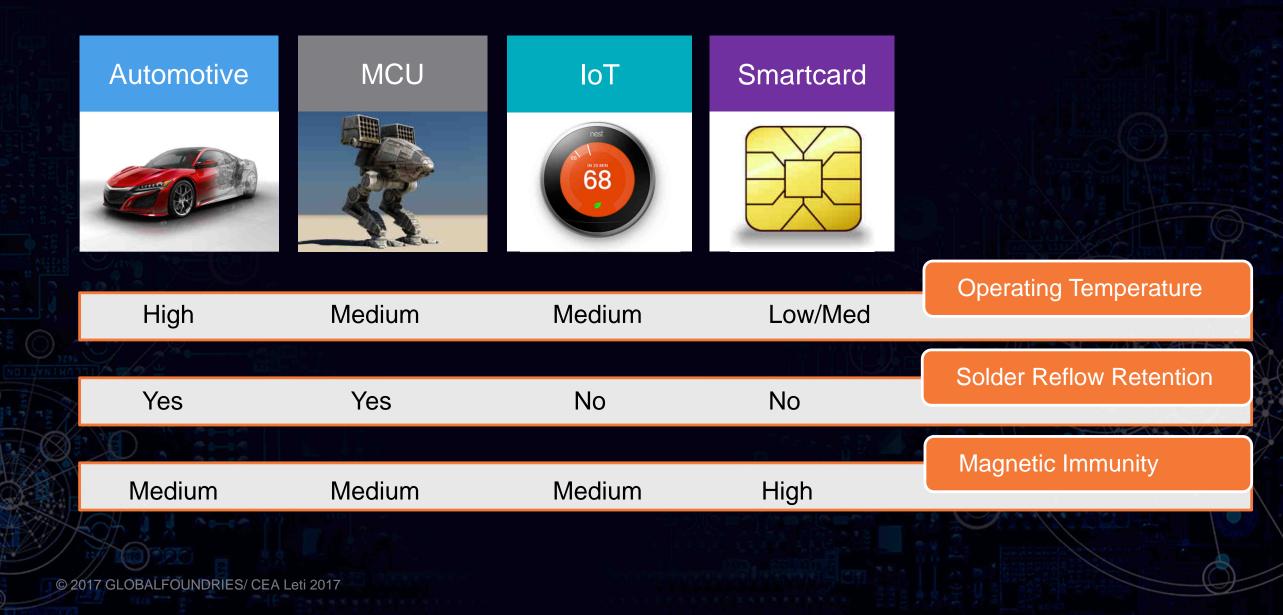

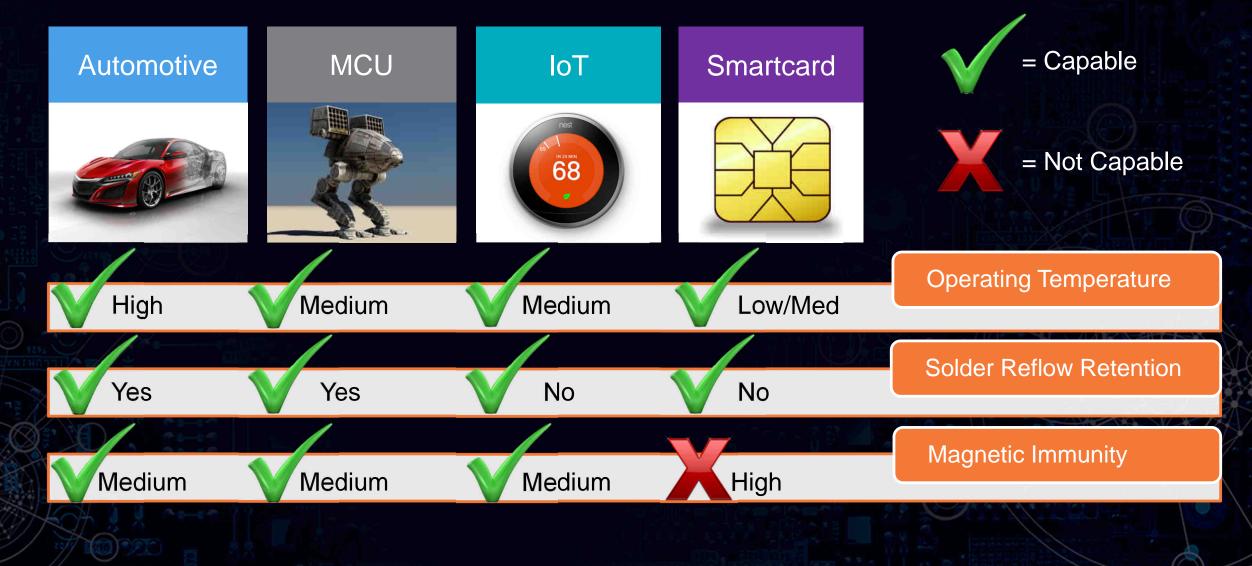

### Embedded Memory: eMRAM market requirements

# eMRAM Limitations

#### eMRAM Technical Barriers

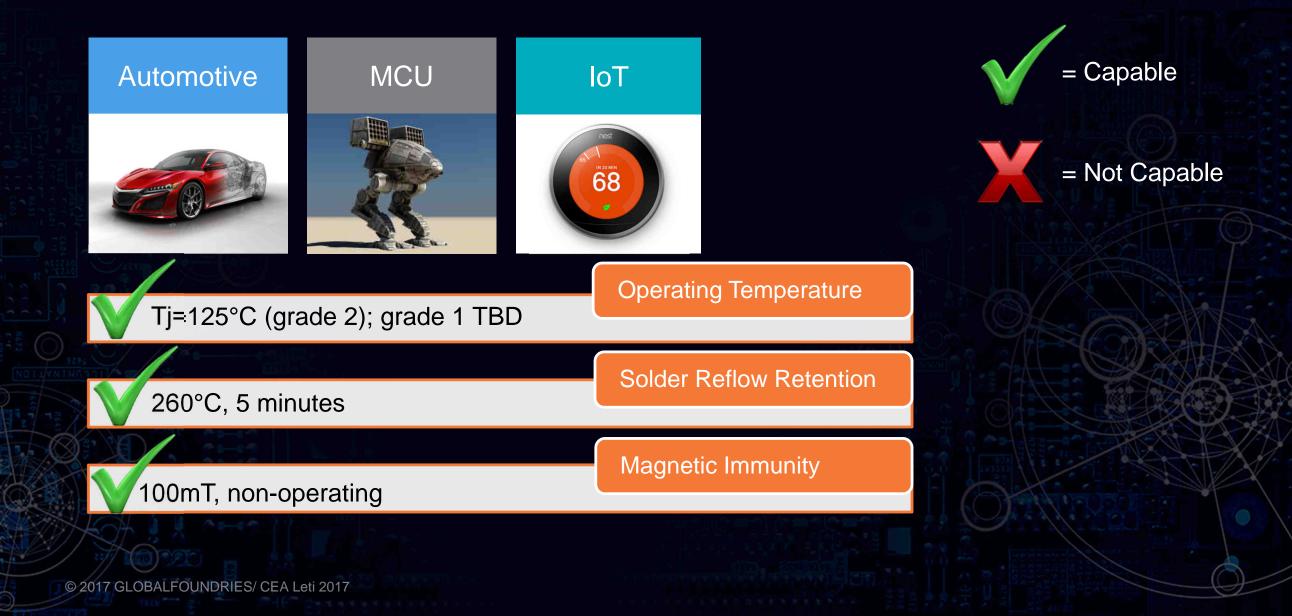

### **Operating Temperature**

- Small memory window (TMR)

- Larger/complicated sense amp; Slower read speed

### Solder Reflow Retention

- 260°C, 5 min data retention

- Must raise Eb, without increasing bitcell size

- Difficult challenge; requires tradeoffs

### Magnetic Immunity

- New issue unique to magnetic memory

- 500 Oe 1000 Oe (100mT) without shielding

- Customer specs still evolving

#### Embedded Memory: eMRAM capabilities

#### Embedded Memory: eMRAM capabilities

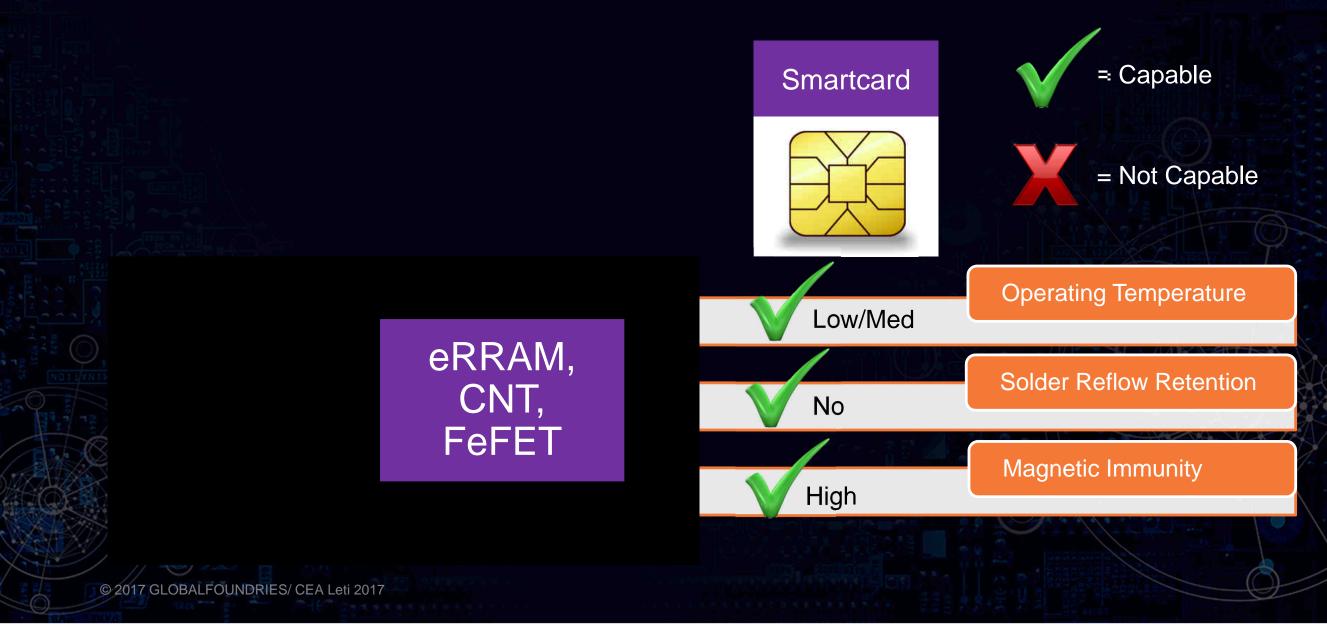

#### Embedded Memory: non-eMRAM Opportunity

# eMRAM Enabling Features

#### Differentiation using Design

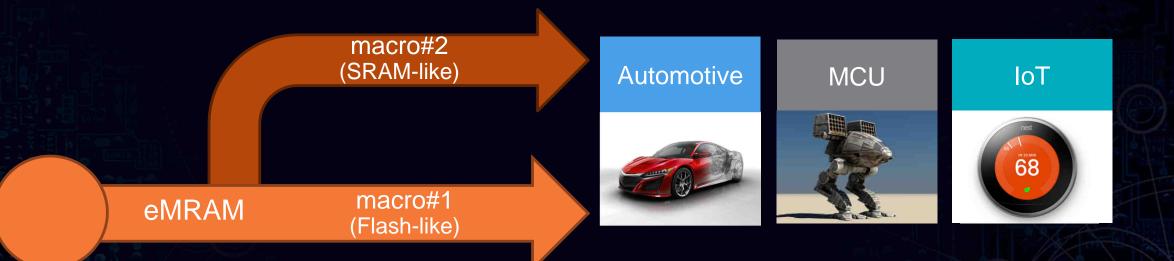

#### eMRAM: Two functions on the same wafer

• By varying the cell configuration and macro design, both code/data storage and working data functions are achieved!

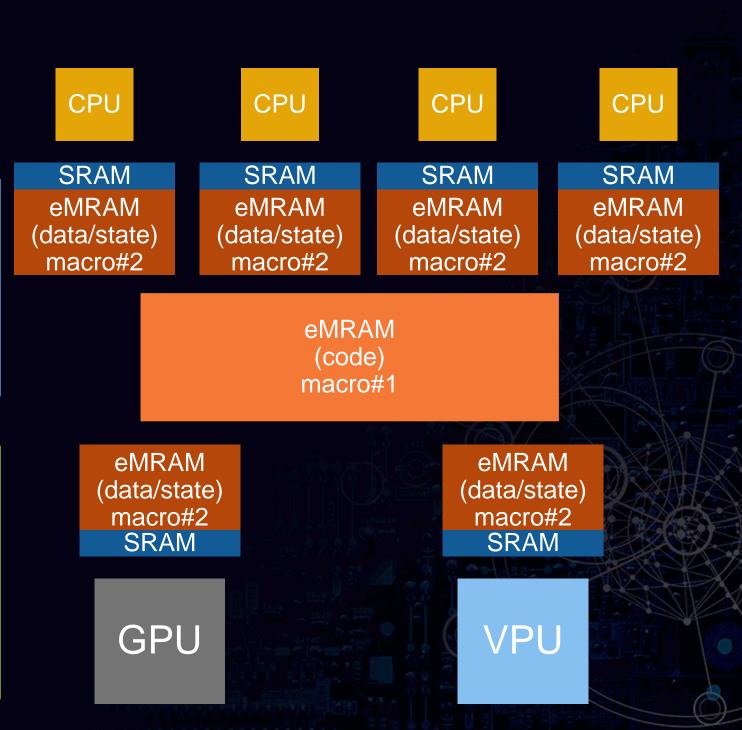

### Versatility of eMRAM enhances Architecture

#### Architecture

- Change around eMRAM

- Both code and data/state

- Great for normally-off systems

### **Energy Savings**

- New ultra-efficient memory subsystem

- Power cycle without time or energy penalty

- 1/3<sup>rd</sup> power of standard SOC

|                           | eFlash               | eMRAM<br>(macro#1)                  | eMRAM<br>(macro#2)                  |

|---------------------------|----------------------|-------------------------------------|-------------------------------------|

| Speed (Rd/Wr)             | 10ns / 20us          | 25ns /200ns                         | 12.5ns /40ns                        |

| Cell size                 | 40F <sup>2</sup>     | 45F <sup>2</sup>                    | 70F <sup>2</sup>                    |

| Endurance                 | 10 <sup>5</sup>      | <b>≈</b> 10 <sup>8</sup>            | <b>≈10</b> <sup>10</sup>            |

| Data Retention            | >20 years            | 10 years                            | 10 years                            |

| Solder reflow (260C/5min) | Yes                  | Yes                                 | Yes                                 |

| Op Temp (Tj)              | 155C<br>Auto grade 1 | 125C<br>Industrial/<br>Auto grade 2 | 125C<br>Industrial/<br>Auto grade 2 |

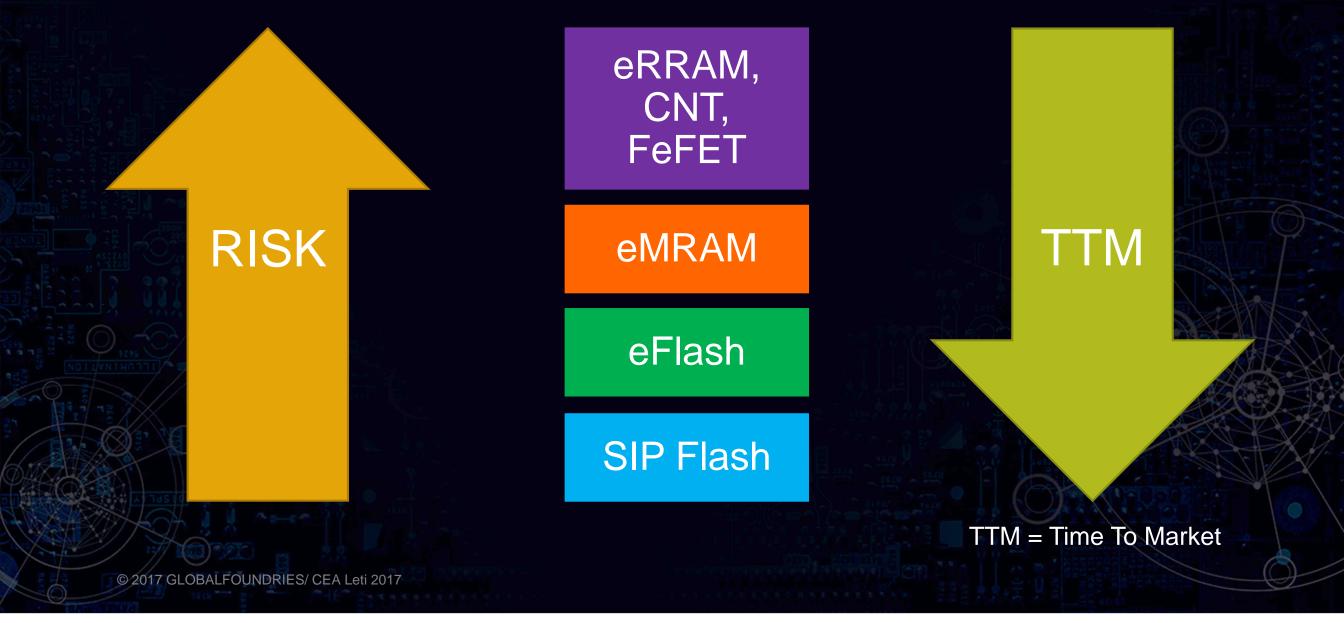

# **Competing Solutions**

### eMRAM competing solutions

### **Cost Effective Manufacturing**

#### eMRAM Commercial Barriers

### Capital Equipment

- Expensive, unique eMRAM CapEx

- Deposition, etch, magnetic anneal

### **Throughput and Yield**

- Must achieve 20+ wph

- Must achieve typical 95%+ yield; <1E<sup>-6</sup> RBER

### Customers

- Will not pay for write speed/endurance benefits

- Want a cost reduction vs. eFlash

- Taking a schedule and reliability risk

# As an industry, we are not there yet!

"Still a desire for higher throughput and lower complexity/cost"

### Future eMRAM

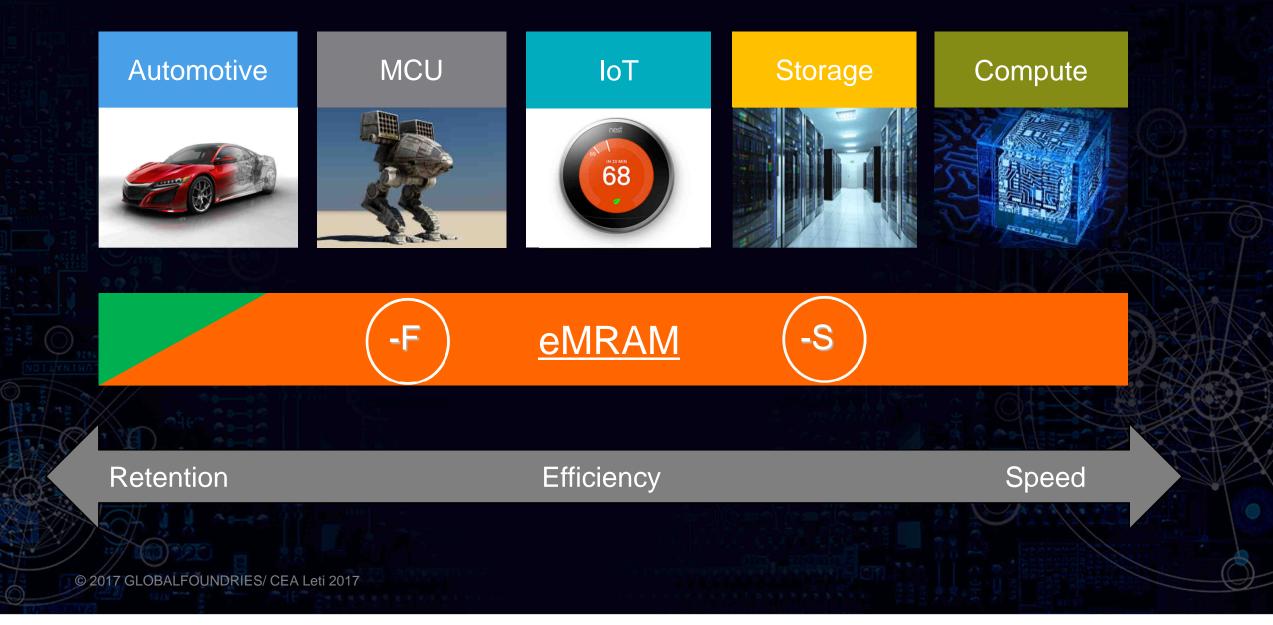

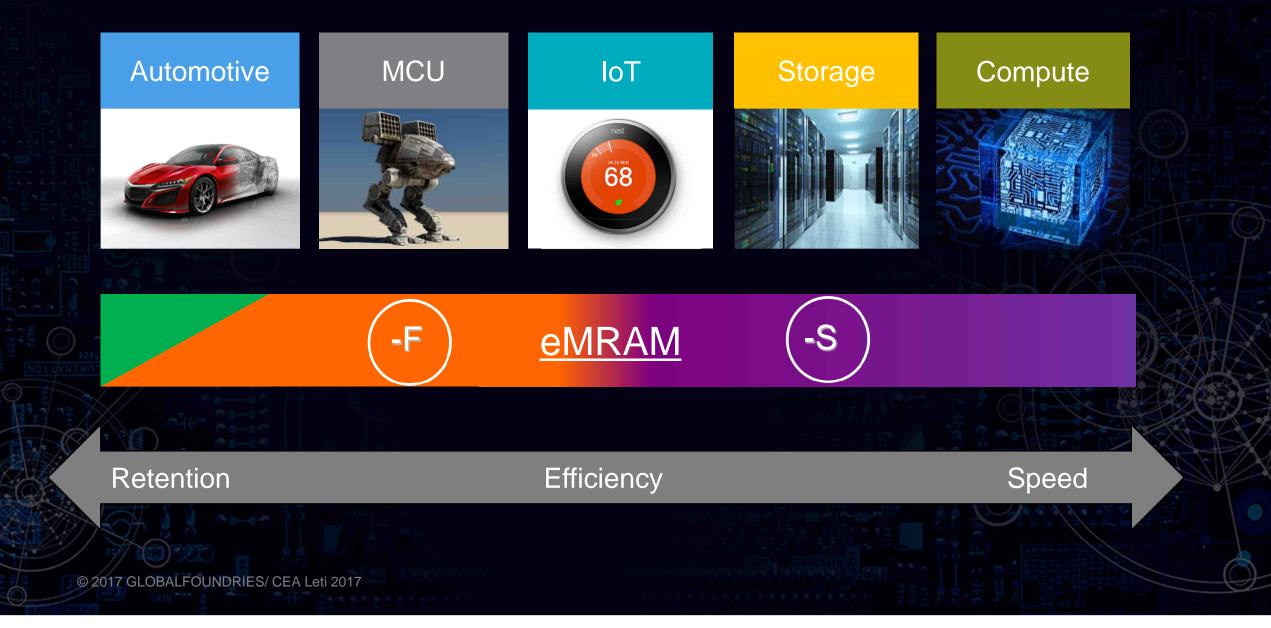

### Embedded Memory: eMRAM types

### Embedded Memory: eMRAM types

### Embedded Memory: eMRAM types

|                           | eFlash               | eMRAM-F<br>(macro#1)                | eMRAM-F<br>(macro#2)                | eMRAM-S               |

|---------------------------|----------------------|-------------------------------------|-------------------------------------|-----------------------|

| Speed (Rd/Wr)             | 10ns / 20us          | 25ns /200ns                         | 12.5ns /40ns                        | ≈ 5ns / 10ns          |

| Cell size                 | 40F <sup>2</sup>     | 45F <sup>2</sup>                    | 70F <sup>2</sup>                    | 100-120F <sup>2</sup> |

| Endurance                 | 10 <sup>5</sup>      | <b>≈1</b> 0 <sup>8</sup>            | <b>≈10</b> <sup>10</sup>            | ≈10¹₄                 |

| Data Retention            | >20 years            | 10 years                            | 10 years                            | 1 month               |

| Solder reflow (260C/5min) | Yes                  | Yes                                 | Yes                                 | No                    |

| Ор Тетр (тј)              | 155C<br>Auto grade 1 | 125C<br>Industrial/<br>Auto grade 2 | 125C<br>Industrial/<br>Auto grade 2 | 105C<br>Enterprise    |

© 2017 GLOBALFOUNDRIES/ CEA Leti 2017

#### How much Endurance is enough for eMRAM-S?

Systematic Validation of 2x nm Diameter Perpendicular MTJ Arrays and MgO Barrier for Sub-10 nm Embedded STT-MRAM with Practically Unlimited Endurance J.J. Kan<sup>1,a</sup>, C. Park<sup>1</sup>, C. Ching<sup>2</sup>, J. Ahn<sup>2</sup>, L. Xue<sup>2</sup>, R. Wang<sup>2</sup>, A. Kontos<sup>2</sup>, S. Liang<sup>2</sup>, M. Bangar<sup>2</sup>, H.Chen<sup>2</sup>, S. Hassan<sup>2</sup>, S. Kim<sup>1</sup>, M. Pakala<sup>2,b</sup>, and S. H. Kang<sup>1</sup>

> <sup>1</sup>Qualcomm Technologies, Inc., San Diego, California 92121, USA. E-mail: <sup>a</sup>jkan@qti.qualcomm.com <sup>2</sup>Applied Materials, Inc., Sunnyvale, California 94085, USA. E-mail: <sup>b</sup>mahendra\_pakala@amat.com

For typical cache use cases, an average time exists between successive writes to the same cache block. From reported workload simulations, very write-intensive applications (> 50% write vs. read) have a median write interval of ~ 10 ms (20 % of bits have  $\Delta t \ge 40$  ms) [4]. This implies that a write endurance of 10<sup>11</sup> cycles would be sufficient for 30 years of uniform write operations. Alternatively, one could assume a 32 MB STT-MRAM (64-bit I/O, 5 ns write cycle time) subjected to a constant write traffic of 1.6 GBps. With uniform writing, a lifetime of 63 years would be expected for an endurance of only 10<sup>11</sup> cycles, substantially less than the 10<sup>15</sup> predicted for our worst 1ppm. Source: IEDM 2016; J.J. Kan, et al; Qualcomm

© 2017 GLOBALFOUNDRIES/ CEA Leti 2017 © 2017 GLOBALFOUNDRIES/ CEA Leti 2017 "Write endurance of 10<sup>11</sup> cycles would be sufficient for 30 years of uniform write operations"

### Future eMRAM

#### Gb densities of NV memory

• Enables real-time analysis of big data

#### Powers intelligent clients

• AR/VR, AI, Autonomous Vehicles

#### NV-logic transformation

Integrate non-volatility directly into logic elements

### Markets & Requirements

eMRAM Limitations

eMRAM Enabling Features

**Competing Solutions**

### **Cost Effective Manufacturing**

### Future eMRAM

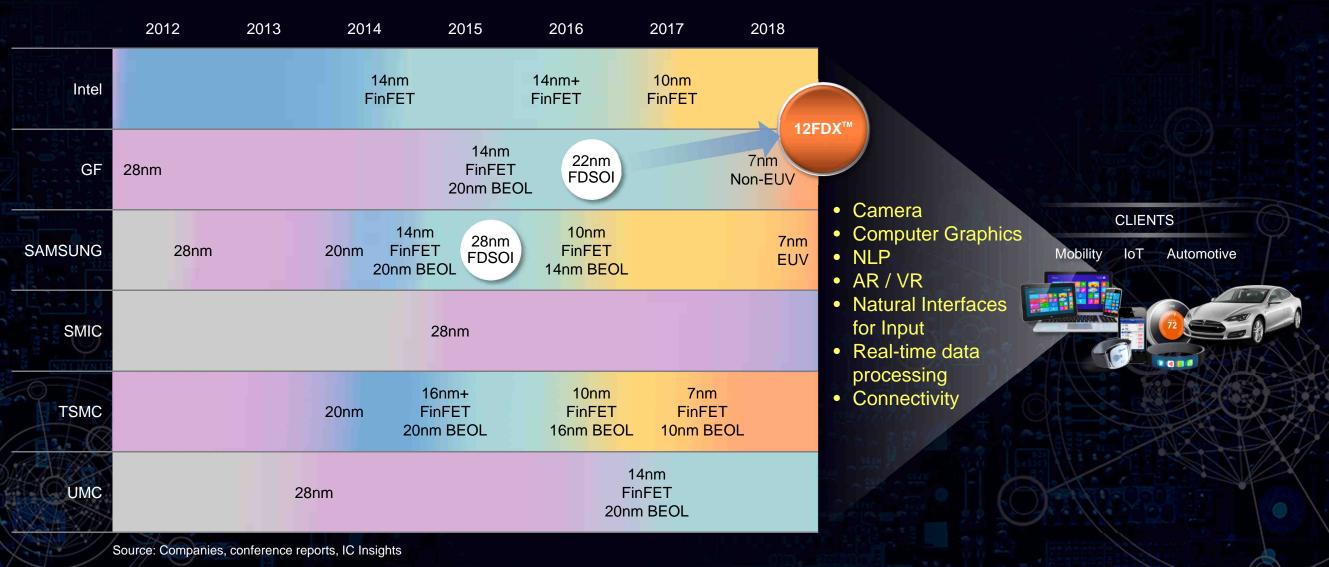

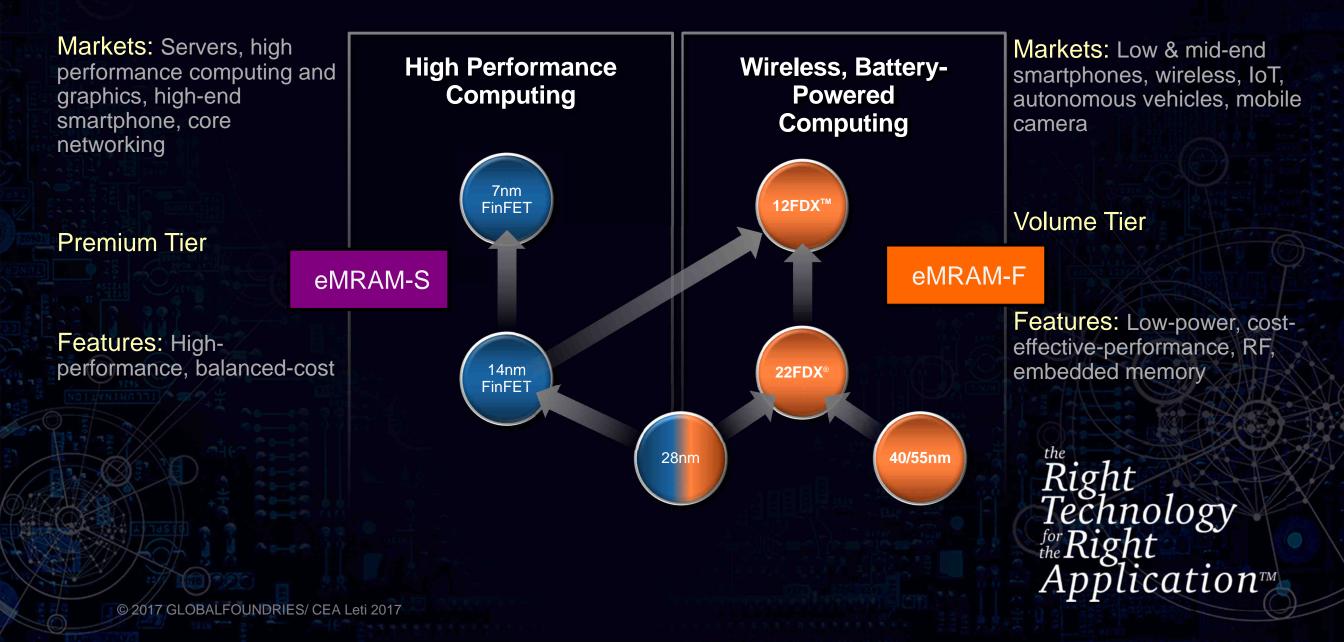

# GLOBALFOUNDRIES Roadmap & eMRAM

### Building Global Scale for FDX<sup>™</sup>

Dresden, Germany Fab 1

- Expanding 22FDX<sup>®</sup> FD-SOI capacity by 40% by 2020

- Developing 12FDX<sup>™</sup> FD-SOI technology with tape-outs 2H 2018

6 Per

Chengdu, China Fab 11

- New 300mm fab- in partnership with Chengdu Municipal Government

- Existing 180/130nm technologies, production starting 2H 2018, then 22nm in 2H19

- Multi-fab sourcing for assurance of supply

- Multiple substrate vendors for robust supply chain

- Local commitment to China industry growth © 2017 GLOBALFOUNDRIES/ CEA Leti 2017

### **FD-SOI Will Become Standard for the Volume Tier**

### **GLOBALFOUNDRIES CMOS Roadmap**

### GF eMRAM: High Reliability, Broad Markets

GLOBALFOUNDRIES and Everspin continue to drive embedded MRAM (eMRAM) forward into the 22nm process node!

For the first time, we are unveiling eMRAM that can retain data through solder reflow at 260C and 10+ years at 125C, plus read/write with outstanding endurance at 125C.

This is a major breakthrough from GLOBALFOUNDRIES and Everspin that enables eMRAM to be used for general purpose MCU's and Automotive SOCs.

Please contact me if you want more information! dave.eggleston@globalfoundries.com

# GLOBALFOUNDRIES® Embedded Memory

Solving your product challenges for the hyperconnected world